미래 메모리 기술, 美·日·대만 등 전 세계 연구 뜨겁다

상변화M, 집적도 향상 신소재 선택소자 개발 초점

저항변화M, 삼성·SK·인텔·파나소닉·마이크론·TSMC 연구활발

■ 연구개발 동향_상변화 메모리

오랜 기초·원천 연구를 통해 상변화 메모리에 사용되는 대표 소재는 저마늄(Ge), 안티모니(Sb), 텔루륨(Te) 원자의 비율이 2:2:5 조성의 삼성분계 칼코지나이드 화합물이다. 상변화 물질의 정립과 명확한 동작 원리의 이해를 바탕으로 높은 기술 성숙도를 보인 상변화 메모리는 동작 전류를 낮출 수 있는 소자 구조설계 연구가 주로 진행되다가 2010년 이후 집적도를 향상할 수 있는 신소재 기반 선택 소자(selector) 개발에 초점이 맞춰져 있다.

1) 국내 동향

삼성전자에서는 2010년 보고서에서 상변화 소재를 제한된 영역에만 증착하고 전류를 공급하는 하부 전극의 크기를 최소화하는 구조(dash-confined)를 제시하였는데, 이는 줄 열의 생성을 극대화하여 20nm 이하 공정기술에서 저전력 메모리 동작이 가능함을 증명했다.

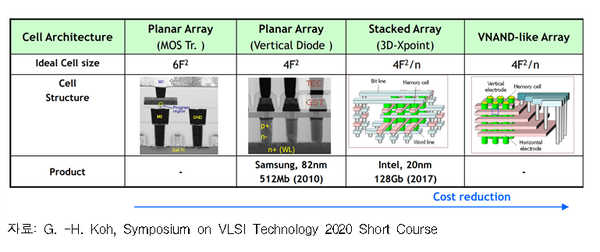

같은 해 삼성전자는 크로스포인트 어레이에서 특정 메모리만을 선택할 수 있는 선택 소자로 3단자 트랜지스터 대신 2단자 실리콘 기반 다이오드를 이용해 82nm의 회로 선폭을 갖는 512Mb 상변화 메모리를 세계 최초로 양산했다. 핸드폰에 탑재하여 상변화 메모리의 저전력 동작으로 20% 이상의 배터리 절감 효과를 확인했다.

2018년 SK하이닉스에서는 미국 인텔(Intel)과 마이크론(Micron)이 2015년 보고한 기술과 유사한 칼코지나이드 소재 기반 선택 소자를 개발하여 2znm 공정기술로 2층으로 적층한 128Gb의 대용량 상변화 메모리 기술을 발표했다.

2) 해외 동향

가. 미국

삼성전자가 양산했던 상변화 메모리의 경우, 단위 소자가 하나의 상변화 메모리와 하나의 다이오드로 되어있다. 인텔과 마이크론은 상변화 메모리의 고집적화를 위하여 3차원 적층 가능한 새로운 2단자 선택 소자를 공동으로 개발했다. 칼코겐 원소가 포함된 이원분계 이상의 칼코지나이드 화합물에서 특정 값 이상의 전압이 인가되면 소자가 켜지고 상당한 전류를 공급하며, 전압을 제거하면 재빠르게 꺼지는 오보닉 문턱 스위칭(Ovonic Threshold Switching) 소자를 이용하였다.

실리콘 다이오드와 달리, 오보닉 문턱 스위칭 소자는 저온 공정이 가능하여, 2015년 20nm 공정기술로 제작된 상변화 메모리를 2층으로 적층한 128Gb의 대용량을 달성했다.

3차원 크로스포인트(3D XPoint)의 기술명과 OptaneTM의 제품명으로 양산하여 다양한 제품군에 적용되고 있다. 2층으로 적층된 1세대 기술을 넘어 현재 4층의 2세대 3차원 크로스포인트 상변화 메모리를 개발 중이고 2021년에 출시할 것을 발표했다.

IBM에서는 2014년부터 인간의 뇌 구조와 기능을 모사하여 병렬 연산이 가능한 차세대 뉴로모픽 컴퓨팅(neuromorphic computing) 기술에 상변화 메모리를 이용하고 있다. 메모리 분야에서는 ‘0’과 ‘1’의 디지털 정보를 이용하는 반면, 뉴로모픽 분야에선 생물학적 시냅스 역할을 하는 아날로그 메모리가 필요하다. 프로그래밍 스킴(programming scheme)과 소자 설계로 상변화 과정을 미세하게 조절하여 아날로그 정보를 확보 후, 상변화 메모리로 구성된 뉴로모픽 시스템으로 필기체 등 패턴 인식 분야에 적용하고 있다.

나. 일본

3차원 적층 형태는 크로스포인트 구조 외에 절연체와 금속을 연속적으로 증착하여 쌓아 올린 후, 홀(hole)을 만들고 식각한 홀 벽면에 메모리 소재를 증착하는 3차원 낸드플래시 구조가 있다.

인텔이 2015년 발표한 크로스포인트 기술을 활용해 적층해나가면 잦은 패턴의 식각으로 오히려 공정비용이 증가하는 단점이 있다. 일본 히타치(Hitachi) 중앙연구소는 2012년 공정비용을 절감할 수 있는 4층의 3차원 낸드 플래시 구조에 상변화 메모리를 적용한 결과를 발표하였다.

■ 저항 변화 메모리

1) 국내 동향

2004년 삼성전자에서 180㎚ CMOS(Complementary Metal-Oxide Semiconductor) 플랫폼에 제작된 니켈 산화물(NiO)을 이용한 저항 변화 메모리 발표 이후, 전 세계적으로 학계와 산업계의 관심도가 폭발적으로 증가하였다.

세계 메모리 반도체 1위 삼성전자의 2004년도 디램과 낸드플래시 공정기술 수준은 80nm 및 60nm였다. 삼성종합기술원과 함께 국부적인 전도성 필라멘트에 의해 메모리 특성이 나타남을 밝혀, 저전력 고속 동작이 10nm 이하의 소자 크기에서도 가능할 것으로 판단돼 기존 메모리를 대체할 수 있는 유력한 후보가 되었다.

결함을 이용하기 때문에 많은 소재 탐색 및 물리적 동작 원리 이해에 대한 연구가 오랜 기간 수행되었고, 2010년 이후부터는 하프늄 산화물(HfO2)과 탄탈럼 산화물(Ta2O5)로 소재의 후보군이 좁혀진 상태이다.

2012년 SK하이닉스에서는 미국 HP와 공동기술개발(joint development) 협약을 맺고 54nm 공정기술로 제작한 탄탈럼 산화물 기반 저항 변화 메모리를 선택 소자 없이 2층으로 적층한 2Mb 칩을 개발하였다.

이후 2017년 실리콘 산화물 기반의 2단자 선택 소자를 개발하여 25nm 공정기술로 제작된 저항 변화 메모리를 발표했다.

하지만 무작위한 결함의 움직임을 제어하기 어려워 대면적 웨이퍼에서 메모리 소자 간 특성 불균일에 의해 신뢰성 문제가 발생해 제품 양산에는 문제가 있다. 최근 국내 대학기관에서는 높은 신뢰성을 요구하는 메모리 기술보다, 어느 정도 오차를 허용하는 뉴로모픽 기술로 방향을 선회하여 아날로그 메모리를 위한 소재 및 소자 구조설계 연구가 진행 중이다.

2) 해외 동향

가. 미국

미국의 스타트업(Start-up) 아데스토 테크놀로지스(Adesto Technologies)는 2013년 이동도가 높은 실버(Ag) 이온을 활용하여 낮은 전압에서 구동하는 저항 변화 메모리를 개발했다. 2016년 130nm CMOS 플랫폼을 사용한 128kb∼1Mb의 1세대 메모리를 헬스케어용 사물 인터넷 제품에 탑재했고 기존 대비 50∼100배 적은 에너지 소모로 배터리 사용시간을 증가시켰다.

일본 타워재즈(TowerJazz)의 45nm CMOS 플랫폼을 이용하여 2세대 메모리 기술을 양산하였고, 2018년에는 국내 동부하이텍의 130/90nm CMOS 플랫폼에 접목하기로 라이센스 협의를 하였다.

2020년 2월 아데스토는 영국 소재 반도체 업체인 다이얼로그 반도체(Dialog Semiconductor)에 인수되었다.

메모리 기술만을 보유한 스타트업의 경우 로직용 CMOS 플랫폼을 보유한 반도체 위탁 생산 업체(foundry)에 의뢰하여 제품을 개발하는 반면, 종합 반도체 업체(Integrated Device Manufacturer, IDM)인 인텔은 2019년 탄탈럼 산화물 기반 저항 변화 메모리를 자사의 22nm 핀펫(FinFET) 플랫폼에 직접 도입하였는데, 4Mb 칩에서 5나노초의 굉장히 빠른 읽기 속도 결과를 보인다고 발표했다.

나. 일본

2008년 파나소닉(Panasonic)은 탄탈럼 산화물에서 열역학적으로 안정한 결정상의 존재로 메모리 쓰기/지우기 동작이 109번 이상 가능함을 보고하였다. 2013년 180nm CMOS 플랫폼에 적용한 64Kb 저항변화 메모리를 세계 최초로 상용화하였다.

미세화 공정을 진행하여 2016년 후지쯔(Fujitsu)의 40nm CMOS 플랫폼으로 4Mb 저항변화 메모리를 양산했다. 2012년 집적도 향상을 위해 트랜지스터 대신 실리콘 질화물(SiN) 기반 2단자 선택 소자를 개발하여 메모리가 2층으로 적층된 8Mb 크로스포인트 구조를 발표하였다.

한편 파나소닉에서 탄탈럼 산화물을 이용한 메모리 특성 발표 이후 삼성전자와 미국 HP에서도 동일 소재를 채택했고, 삼성종합기술원은 2011년, 낸드플래시보다 106배 좋은 내구성을 보인다고 발표했다.

메모리 성능 개선을 위해 소재 개발의 중요성을 보여주는 대표적인 사례라고 볼 수 있다. 2013년 키옥시아(Kioxia, 舊.도시바)는 웨스턴디지털(Western Digital, 舊.샌디스크)과 공동으로 2단자 실리콘 다이오드를 적용하여 24nm 공정기술로 제작되고 저항변화 메모리가 2층으로 적층된 32Gb의 대용량 메모리를 발표하였다.

소니(Sony)는 2007년 이동도 높은 구리(Cu) 이온을 이용해 나노 초(sec.) 수준의 고속 동작이 가능한 저항 변화 메모리를 보고하였고, 2011년 180nm CMOS 플랫폼에 적용한 4Mb 칩을 발표했다.

2014년에는 미국 마이크론의 디램에서 사용된 최신 27nm 베리드(buried) 트랜지스터 소자/설계 기술에 소니가 개발한 메모리를 적용하여 16Gb 저항변화 메모리를 구현했다.

메모리 용량과 크기 관점에선 디램이 차지하는 면적과 유사하지만, 비휘발성으로 저전력과 마이크로초 수준의 고속 읽기/쓰기 동작이 가능해져 디램의 성능을 보완하는 것을 목표로 한다. 최근 소니는 독자적으로 개발한 오보닉 문턱 스위칭 소자를 선택 소자로 이용하여 3차원 적층 형태의 고집적 메모리를 개발 중이다.

다. 대만

세계 최대 반도체 위탁생산 기업인 TSMC는 2017년 자사의 40nm CMOS 플랫폼에 적용한 저항 변화 메모리 기술의 위험생산(risk production)을 했고 2018년 고객사에서 요구한 125oC 고온에서의 10년 동안 메모리 유지성과 104번의 쓰기/지우기 반복 내구성 검증을 완료했다. 최근에는 22㎚ CMOS 플랫폼에 적용된 하프늄 산화물 기반 저항 변화 메모리를 고객에게 제공하는 위탁생산 서비스를 시작했다.

▲ 그림 1 선택 소자와 메모리 구조에 따른 상변화 메모리의 집적도 및 원가 절감

▲ 그림 1 선택 소자와 메모리 구조에 따른 상변화 메모리의 집적도 및 원가 절감