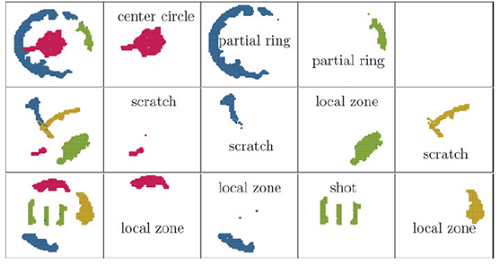

▲ 여러형태의 혼합된 불량칩 패턴과 각 특정 패턴으로 군집화된 불량칩 패턴

▲ 여러형태의 혼합된 불량칩 패턴과 각 특정 패턴으로 군집화된 불량칩 패턴국내 연구진이 한 개의 반도체 기판에서 존재하는 다양한 형태의 불량 패턴을 효과적으로 탐지하는 방법을 찾았다.

KAIST는 김희영 산업및시스템공학과 교수 연구팀이 반도체 기판 내 여러 형태의 혼합된 불량 칩 패턴을 찾아 군집화하는 기술을 개발했다고 14일 밝혔다

반도체 기판은 가공이 끝나면 기판 내 각 칩의 불량 여부를 테스트하는 과정을 거친다. 불량칩은 공정 이상 원인에 따라 보통 특정한 패턴(원, 스크래치 등)을 보이며 분포하기에 이러한 불량 분포 패턴을 분석해 원인을 파악하는 것이 중요한 과제로 꼽히고 있다.

최근 반도체 제조 공정이 점점 복잡해지면서 한 기판 안에 여러 형태의 불량칩 패턴이 혼재되는 사례가 증가하고 있다.

이에 연구팀은 다수의 불량칩 패턴을 효과적으로 파악하기 위해 일정 패턴을 형성하고 있는 불량칩을 선택한 후 여러 개의 특정 패턴으로 군집화하는 방법을 제시했다.

연구팀은 무작위 분포가 아닌 특정 패턴을 형성하고 있는 불량칩을 효과적으로 탐지할 수 있는 CPF(connected-path filtering) 기술을 개발했다. CPF는 특히 스크래치 형태로 분포된 불량칩 탐지에 탁월한 성능 향상을 보였다.

탐지한 불량칩을 다수의 패턴별로 군집화하는 과정에서는 사전에 서로 다른 몇 개의 패턴이 혼재됐는지 알지 못한다는 점과 각 패턴이 복잡한 모양을 가진다는 점이 어려움으로 남아 있었다.

이를 해결하기 위해 연구팀은 ‘무한 비선형 혼합 모형(infinite warped mixture model)’을 이용함으로써 군집화 과정에서 데이터가 스스로 군집 수를 결정할 수 있도록 했다.

또한 복잡한 모양의 패턴을 바로 이용하는 대신 은닉 공간에서의 단순한 모양의 패턴을 이용해 보다 효과적으로 군집화하는 데 성공했다.

연구팀은 SK하이닉스의 실제 반도체 데이터를 활용해 제안된 방법을 검증함으로써 실제 반도체 제조 현장 문제를 효과적으로 해결할 수 있음을 확인했다.

한편, 이번 연구 결과는 산업공학 분야 저명 국제 학술지 ‘IISE Transactions’ 2월호에 게재됐다. 특히 이 논문은 특집 기사(featured article)로 선정돼 ‘ISE(Industrial and Systems Engineering)’ 매거진 1월호에도 게재됐다.