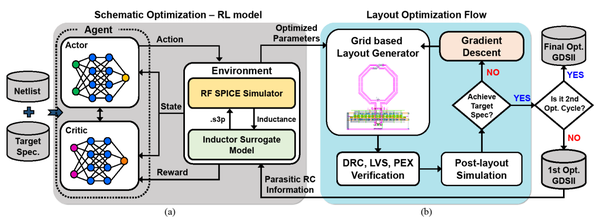

▲ LC-VCO 자동 설계에 있어 (a)강화학습 에이전트가 회로 시뮬레이션 환경과 소통하며 최적의 변수를 탐색한다. (b)회로 설계 결과를 바탕으로 레이아웃을 생성한 뒤, 기생 효과를 반영한 시뮬레이션을 거쳐 경사하강법으로 배선과 구조를 반복 보정해 최종 설계를 완성한다.

▲ LC-VCO 자동 설계에 있어 (a)강화학습 에이전트가 회로 시뮬레이션 환경과 소통하며 최적의 변수를 탐색한다. (b)회로 설계 결과를 바탕으로 레이아웃을 생성한 뒤, 기생 효과를 반영한 시뮬레이션을 거쳐 경사하강법으로 배선과 구조를 반복 보정해 최종 설계를 완성한다.

반도체 설계 전문가가 수주에서 수개월씩 걸려 작업하던 고성능 통신 반도체 회로 설계를 단 하루 만에 끝낼 수 있는 인공지능(AI) 기술이 개발돼 차세대 공정으로의 신속한 전환에 기여할 전망이다.

UNIST 전기전자공학과 윤희인 교수와 경북대학교 송대건 교수팀은 통신 회로인 LC 전압제어 발진기(LC-VCO)를 회로 설계 단계부터 실제 칩에 넣는 물리적 레이아웃까지 자동으로 설계해주는 AI 모델을 개발했다고 지난 5일 밝혔다.

LC-VCO는 5G 같은 고속 통신 시스템에서 주파수를 만들어내는 반도체 회로다. 신호 잡음과 전력 소모를 줄이기 위해서는 인덕터, 트랜지스터 크기와 같은 변수를 잘 조합해 회로를 설계해야 하는데, 설계된 회로를 실제 칩 안으로 옮기기 위한 레이아웃 설계 단계에서는 회로 설계 단계의 조합이 깨지기 쉽다. 배선 굵기와 소자 배치에 따라 기생 효과가 더해지면서 주파수와 잡음 특성이 다시 달라질 수 있기 때문이다.

연구팀이 개발한 모델은 회로 설계와 레이아웃 설계를 통합해 최적화할 수 있다. 회로 설계 단계에서는 강화학습을 적용해 설계 변수들을 바꿔가며 목표 주파수와 성능을 만족하는 조합을 찾도록 했다.

실제 칩 구조가 결정되는 레이아웃 단계에서는 성능이 더 좋아지는 방향을 따라 설계 값을 조금씩 조정해 최적의 조건을 찾아가는 경사하강법을 이용해 배선 폭과 간격 같은 물리적 설계 변수를 성능이 개선되는 방향으로 반복적으로 보정했다.

연구팀은 “회로도 설계와 물리적 배치를 개별적으로 최적화하던 기존 방식을 대신 AI가 두 단계를 통합적으로 관리하도록 한 기술”이라고 설명했다.

설계 과정에서 가장 시간이 오래 걸리는 인덕터는 딥러닝 기반 예측을 활용해 전체 설계 시간을 크게 줄였다. 설계자의 반복적인 전자기 시뮬레이션이 필요하던 작업을 단 몇 밀리초(ms) 만에 완료된다.

실험 결과, 기존의 자동 설계 방식이 약 119시간 소요되던 작업을 단 28.5시간 만에 완료해 설계 시간을 76% 이상 단축했다. 성능 지수(FoM) 또한 기존 연구 대비 월등히 우수한 결과를 보였다.

또한 전이 학습이 적용돼 반도체 나노 공정 노드가 바뀌어도 기존에 학습한 내용을 바탕으로 설계를 이어갈 수 있다. 예를 들어 65nm 공정으로 학습한 AI는 40nm나 28nm 공정에서도 처음 학습에 필요했던 데이터의 약 10%만 추가로 활용해 설계를 수행할 수 있다.

연구팀은 LC-VCO뿐만 아니라 다양한 아날로그/RF 회로 설계 자동화로 기술을 확장해 나갈 예정이다.

연구팀은 “5G·6G 통신과 AI 칩의 핵심 부품인 주파수 생성 회로의 성능은 높이면서 설계 비용은 크게 낮출 수 있을 뿐만 아니라 중장기적으로 반도체 설계 인력 부족 문제를 해결하고 차세대 공정으로의 전환 속도를 획기적으로 앞당길 수 있는 도구”라고 기대했다.

한편 연구 결과는 IEEE 반도체 회로 공학회에서 발행하는 권위 학술지인 ‘IEEE 집적회로 및 시스템 설계자동화(TCAD’에 4월 3일 온라인 공개됐다.

연구는 과학기술정보통신부와 한국연구재단, 교육부, 산업통상부, 반도체설계교욱센터(IDEC), 삼성전자, ㈜액시온 등의 지원 및 과기정통부와 정보통신기획평가원(IITP)의 ‘지역지능화혁신인재양성사업’의 지원으로 수행됐다.